性能指标

相位噪声、杂散以及瞬态响应

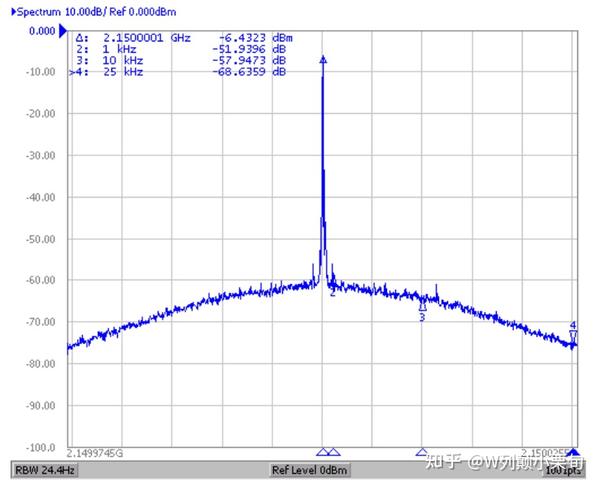

相位噪声

在频域中,这通常被认为是噪声功率相对于载波功率的密度

频谱分析仪测试相位噪声的一个示例。

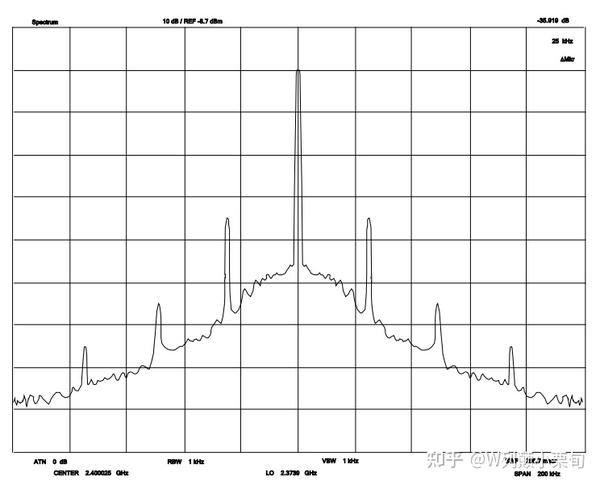

杂散

杂散可以被认为是集中在与载波的特定偏移处的噪声。

杂散有很多种,它们可能有多种原因,但其中大多数发生在非常可预测的偏移处。 杂散倾向于出现在鉴频鉴相器频率、输入参考频率、通道间隔和几分之一通道间隔的倍数处。

瞬态响应和锁定时间

锁定时间通常被认为是在 N 分频器值改变后 PLL 稳定到给定频率容差所需的时间量。锁定时间定义可以扩展到包含相位扰动或容差表示为相位误差而不是频率误差的情况。

锁定时间是 PLL 改变频率所需的时间, 当 PLL 切换频率时,无法传输数据,因此 PLL 的锁定时间必须锁定足够快,以免降低数据速率。 锁定时间也可能与功耗有关。

软件改动

修改pll分频系数, 测试响应时间

CRU/Power 测试 case

| CRU/Power | 测试关闭uart0 时钟 | SOC相关 | 可选 | 不测 | 不测 | test_disable_uart0 | 测试关闭uart0 时钟, 观察uart0 是否打印log, 示波器看uart0 时钟是否关闭, 测试空载电流 |

|---|---|---|---|---|---|---|---|

| CRU/Power | 测试开启uart0 时钟 | SOC相关 | 可选 | 不测 | 不测 | test_enable_uart0 | 测试开启uart0 时钟,观察uart0 是否打印log, 示波器看uart0 时钟是否关闭,测试空载电流 |

| CRU/Power | 测试关闭uart1 时钟 | SOC相关 | 可选 | 不测 | 不测 | test_disable_uart1 | 测试关闭uart1 时钟,观察uart1 是否打印log, 示波器看uart1 时钟是否关闭,测试空载电流 |

| CRU/Power | 测试开启uart1 时钟 | SOC相关 | 可选 | 不测 | 不测 | test_enable_uart1 | 测试开启uart1 时钟,观察uart1 是否打印log, 示波器看uart1 时钟是否关闭,测试空载电流 |

| CRU/Power | 测试关闭uart2时钟 | SOC相关 | 可选 | 不测 | 不测 | test_disable_uart2 | 测试关闭uart2时钟,观察uart2 是否打印log, 示波器看uart2 时钟是否关闭,测试空载电流 |

| CRU/Power | 测试开启uart2 时钟 | SOC相关 | 可选 | 不测 | 不测 | test_enable_uart2 | 测试开启uart2 时钟,观察uart2 是否打印log, 示波器看uart2 时钟是否关闭,测试空载电流 |

| CRU/Power | 测试关闭ao qspi0 时钟 | SOC相关 | 可选 | 不测 | 不测 | test_ao_qspi_disable | 测试关闭ao qspi0 时钟, 测试qspi0 是否正常工作, 示波器看qspi0 时钟是否关闭,测试空载电流 |

| CRU/Power | 测试打开ao qspi0 时钟 | SOC相关 | 可选 | 不测 | 不测 | test_ao_qspi_enable | 测试打开ao qspi0 时钟, 测试qspi0 是否正常工作, 示波器看qspi0 时钟是否关闭,测试空载电流 |

| CRU/Power | 测试关闭pd1 qspi1时钟 | SOC相关 | 可选 | 不测 | 不测 | test_pd1_qspi_disable | 测试关闭pd1 qspi1时钟, 测试qspi1 是否正常工作,,示波器看qspi1 时钟是否关闭,测试空载电流 |

| CRU/Power | 测试打开pd1 qspi1 时钟 | SOC相关 | 可选 | 不测 | 不测 | test_pd1_qspi_enable | 测试打开pd1 qspi1 时钟, 测试qspi1 是否正常工作, 示波器看qspi1 时钟是否关闭,测试空载电流 |

| CRU/Power | 测试关闭ao 外设时钟 | SOC相关 | 可选 | 不测 | 不测 | test_ao_peri_disable | 测试关闭ao 外设时钟, 测试ao 外设是否可以工作, 测试空载电流 |

| CRU/Power | 测试关闭pd1 外设时钟 | SOC相关 | 可选 | 不测 | 不测 | test_pd1_peri_disable | 测试关闭pd1 外设时钟, 测试pd1 外设是否可以工作, 测试空载电流 |

外设相关的疑问

例如pd1上 qspi 有两个时钟的enable mask

pd1_hclk_qspi 和 pd1_refclk_qspi, 很多外设都有两个enable mask, 如果要关闭该外设的时钟,需要设置哪个

- Power_domain_1_bus_clock_enable (offset = 0xc)

- Power_domain_1_peripheral_clock_enable (offset = 0x18)

低功耗模式

ao low power mode

vad 在ao 域上, 可以关闭pd1? ao 需要从active mode 切换到 low power mode上.

ao 切换到 low power mode 后, ao_root_clk 就变成 12.288MHZ了? 在这个频率下vad ip是否可以正常工作? 是用的ao_i2s_clk的频率吗? dma2 是用的ahb_clk吗, 在12.288MHz下是否可以正常工作

ao 从 active mode 切换到 low power mode 除了设置 power_control.bit[0] 外需要哪些前置步骤和后置步骤

通过中断唤醒ao 域时, 是否需要重新走ao 和 pd1 状态机的流程?

ao_active ao_lp 模式怎么相互切换?

ldo怎样enable?

low_power_mode 到 active 状态切换以及开启所有需要工作的时钟 的响应时间

lp->active 状态时的功耗测试

默认时钟频率

1 | CLOCK_FREQ_1M 1000k |